Founder

Codetronix LLC

Oakland, CA

Created product family for rapid development tools for FPGA/ASIC, established funding, established initial customers, developing synchronous and low-power asynchronous circuits

Codetronix LLC

Oakland, CA

Created product family for rapid development tools for FPGA/ASIC, established funding, established initial customers, developing synchronous and low-power asynchronous circuits

Mobius

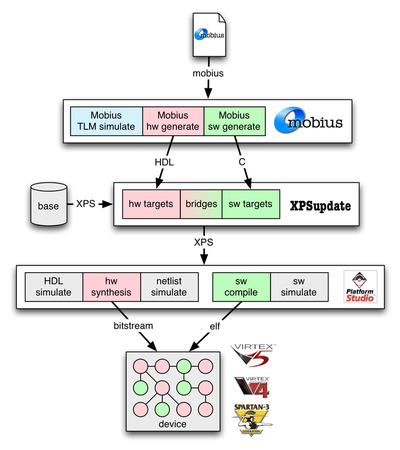

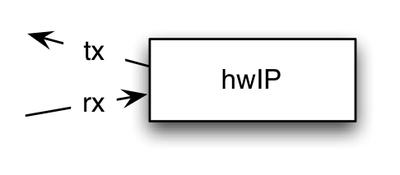

Developed a hw/sw development system optimized for rapid development of FPGA systems. I created a compiler using Ocaml which converted a pascal-like DSL into C, VHDL, and Verilog. Code could be arbitrarily partitioned between 100% software, 100% hardware, or any arbitrary mixture. All generated code was a graph of composable handshaking primitives, resulting in correct-by-construction systems. This Mobius compiler system had commercial, academic and military licensees.

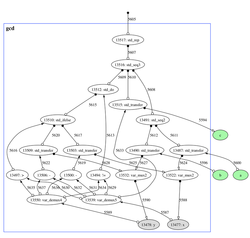

The graph to the left shows a hierarchical compilation of the high level source of the GCD algorithm into simple CDFG nodes. A request signal enters the graph at the top and propagates to a repeater node (while true loop), then to a sequence node with 3 children. First the input parameters a and b are read from channels , then the GCD algorithm iteratively subtracts the smaller from the larger. A leaf node returns an acknowledge signal indicating that the leaf is done. Eventually the GCD algorithm computes an answer and writes it to an output channel c. Then the acknowledge pulse propagates back to the top repeater node and the process begins anew.

Each CDFG node is a simple entity which is proven to be correct. Since the graph is an assembly of nodes, the implementation is correct-by-construction. The graph can be implemented as either HW (VHDL or Verilog) or SW (C with scheduler).

A correct-by-construction version that generated NCL asynchronous circuits was funded by Darpa CLASS working together with Boeing Phantom Works and Camgian Microsystems.

The graph to the left shows a hierarchical compilation of the high level source of the GCD algorithm into simple CDFG nodes. A request signal enters the graph at the top and propagates to a repeater node (while true loop), then to a sequence node with 3 children. First the input parameters a and b are read from channels , then the GCD algorithm iteratively subtracts the smaller from the larger. A leaf node returns an acknowledge signal indicating that the leaf is done. Eventually the GCD algorithm computes an answer and writes it to an output channel c. Then the acknowledge pulse propagates back to the top repeater node and the process begins anew.

Each CDFG node is a simple entity which is proven to be correct. Since the graph is an assembly of nodes, the implementation is correct-by-construction. The graph can be implemented as either HW (VHDL or Verilog) or SW (C with scheduler).

A correct-by-construction version that generated NCL asynchronous circuits was funded by Darpa CLASS working together with Boeing Phantom Works and Camgian Microsystems.

A presentation on the Mobius tools is below.

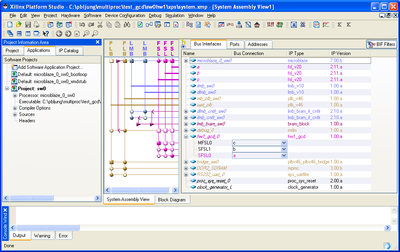

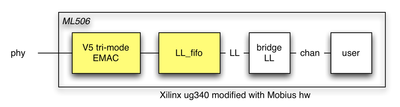

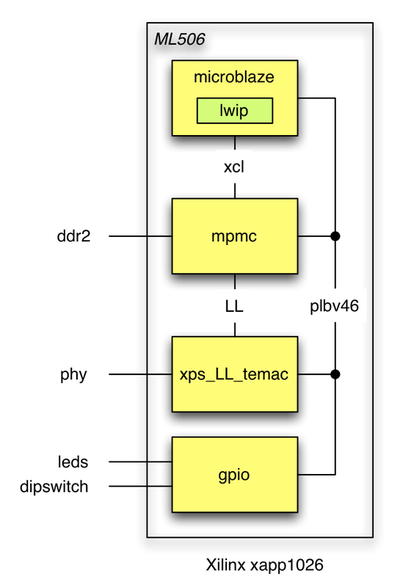

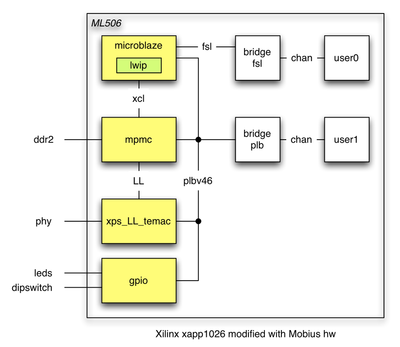

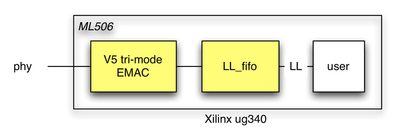

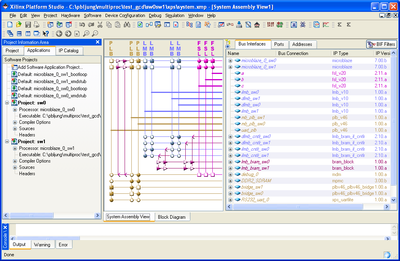

XPSupdate

Building hw/sw systems with the Xilinx XPS tools is challenging. It typically takes 30 man-days to manually create a working system with FSL or PLB interconnects to HW. I used Mobius to generate HW and SW for designated targets, and then augmented a template XPS file (for your particular FPGA or board) adding the Mobius-generated HW, SW and FSL or PLB interconnects. Now the user can proceed as normally and synthesize HW and compile SW to build a XPS project. This lets users create and deploy correct-by-construction complex HW/SW systems in 5 minutes.